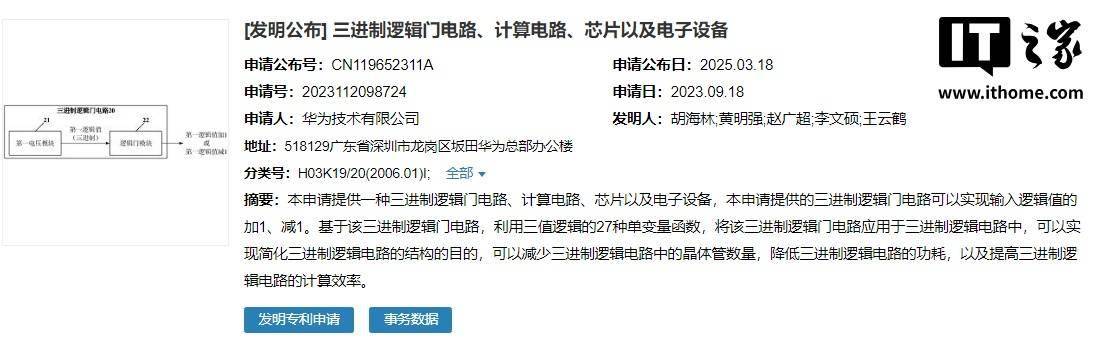

華為近期在技術(shù)創(chuàng)新領(lǐng)域再次邁出重要一步,一項關(guān)于“三進制邏輯門電路、計算電路、芯片及電子設(shè)備”的專利信息由國家知識產(chǎn)權(quán)局正式公布。該專利的申請日期追溯至2023年9月18日,并于次年3月18日由華為技術(shù)有限公司對外揭曉,其公開號為CN119652311A。

據(jù)專利摘要所述,華為此次提出的創(chuàng)新方案聚焦于三進制邏輯門電路的設(shè)計。這一電路的獨特之處在于,它能夠?qū)崿F(xiàn)對輸入邏輯值的加1或減1操作。這一技術(shù)突破,依托于三值邏輯的27種單變量函數(shù),為三進制邏輯電路的應(yīng)用開辟了新路徑。通過巧妙運用這一邏輯門電路,可以顯著簡化三進制邏輯電路的結(jié)構(gòu),有效減少電路中晶體管的數(shù)量,進而降低整體功耗,并大幅提升計算效率。

在當前大數(shù)據(jù)時代背景下,處理海量數(shù)據(jù)對芯片的計算性能提出了更高要求。然而,傳統(tǒng)上通過縮小晶體管尺寸來提升性能的方法已面臨極限。因此,構(gòu)建大規(guī)模集成電路成為提升芯片性能的又一途徑。然而,這種做法同時也帶來了功耗增加和互聯(lián)復(fù)雜度提升的挑戰(zhàn)。在此背景下,三進制邏輯以其提高信息密度的獨特優(yōu)勢,展現(xiàn)出超越二進制邏輯的計算潛力。三進制邏輯電路,憑借其更高的計算性能,成為業(yè)界的關(guān)注焦點。

作為構(gòu)成三進制邏輯電路的基礎(chǔ)單元,三進制邏輯門電路的設(shè)計顯得尤為關(guān)鍵。華為此次推出的專利,正是針對這一核心環(huán)節(jié)的創(chuàng)新嘗試。通過優(yōu)化三進制邏輯門電路的設(shè)計,華為不僅簡化了電路結(jié)構(gòu),還實現(xiàn)了功耗的降低和計算效率的提升,為芯片技術(shù)的發(fā)展注入了新的活力。